## SILICON MICRO- AND NANO-TECHNOLOGIES

**ETCHING**

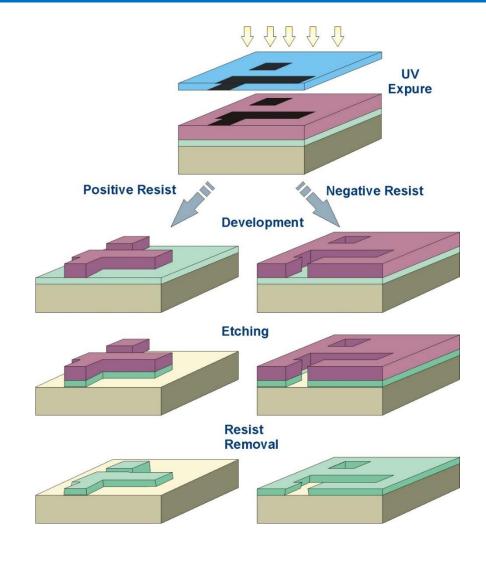

Etching is a process by which material is removed from a substrate of from thin films on the substrate surface. When a mask layer is used to protect specific regions of the wafer surface, the goal of the etching is to "precisely" remove the material which is not covered by the mask

There are two fundamental groups of etching:

- wet etching (liquid-based etchants)

- dry etching (plasma-based etchants, but not only ...)

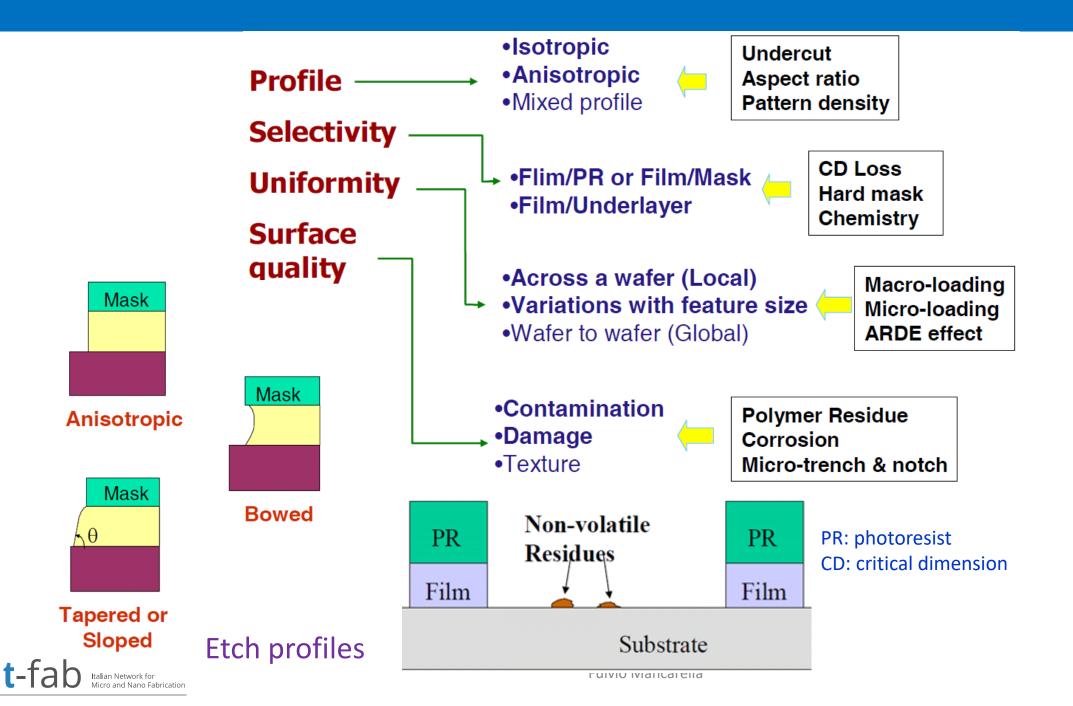

## **ETCHING METRICS**

In general an ideal etch process is not completely attainable

Etching processes are not capable of precisely transfering the pattern established by a mask.

## **PARAMETERS**

**BIAS.** Difference in lateral dimension between the etched image and the mask

**ETCH RATE**. The rate at which the materiale is removed.

**SELECTIVITY**. ratio of the etch rates of one materials over the other. For example, the selectivity is ratio of the etch rate of the layer being etched to the etch rate of the mask or the layer under the layer being etched. Etching with high selectivity is supposed to remove the selected layer entirely without harming the substrate and mask.

### **ETCHING METRICS**

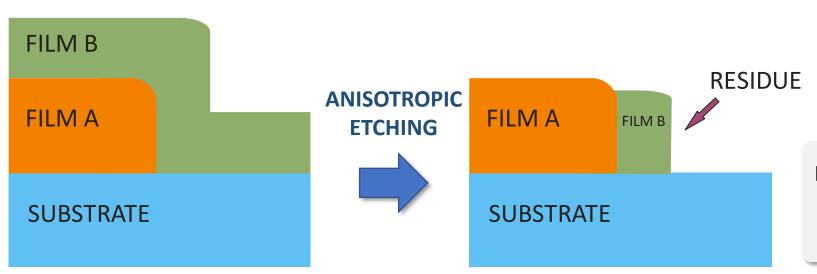

## **ANISOTROPY**

- Isotropic etching has the same etch rate in all directions.

- Anisotropic etching has different etch rates in the lateral and vertical directions.

Anisotropic etching is preferable in semiconductor manufacturing processes and for **micro- nano fabrication**. Most wet etching profiles are isotropic, except for etching crystalline materials, whereas etching profiles of dry etching are anisotropic.

Anisotropy is defined as

$$A=1-\frac{R_L}{R_V},$$

where RL and RV are the lateral and vertical etch rates, respectively. For perfectly anisotropic etching, A is 1. For perfectly isotropic etching, A is 0.

## **ETCHING METRICS: ANISOTROPY**

## **AN EXAMPLE**

**ISOTROPIC (LEFT) AND ANISTROPIC (RIGHT)**

If etching is anistropic, overetching is need to remove residual materials at step

## **ETCHING METRICS: UNDERCUT**

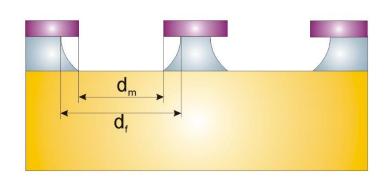

**UNDERCUT.** Lateral distance per side under the mask, as shown in Figure 1. It can be characterized by the etch rate anisotropy A. Sometimes, the etchant will attack the photoresist pattern, which causes an etch bias.

**BIAS**

**UNDERCUT**

**MASK**

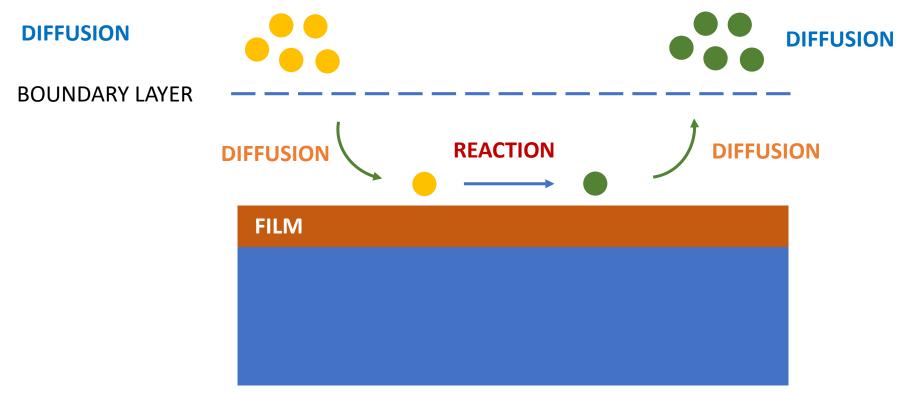

## **ETCHING PROCESS CONSIST OF THREE STEPS**

- Mass transport of reactants (through a boundary layer) to the surface to be etched

- Reaction between reactants and film surface to be etched at the surface

- Mass transport of the reaction products from the surface throught the surface boundary layer

### **WET ETCHING**

- Wet etching was used exclusively till 1970's when feature size >3um.

- For small scale features, large etch bias leads to significant CD (critical dimension) loss.

- For today's IC industry, wet etching is used for noncritical feature sizes.

## **ADVANTAGES**

high selectivity, relatively inexpensive equipment, batch system with high throughput, etch rate can be very fast (many  $\mu$ m/min).

## **DISADVANTAGES**

generally isotropic profile, high chemical usage, poor process control (not so reproducible), excessive particulate contamination.

- The etch rate can be controlled by any of the three serial processes: **reactants transport** to the surface (depends on chemical concentration and stirring...), **reaction rate** (depends on temperature), **reaction products transport** from the surface (depends on stirring...).

- Preference is to have **reaction rate** controlled process because

- Etch rate can be increased by temperature

- Good control over reaction rate temperature of a liquid is easy to control

- Mass transport control will result in non-uniform etch rate: edge etches faster.

- Etchant is often stirred to minimize boundary layer and make etching more uniform.

## WET ETCHING PROCESS: MAIN MIXTURES

| SiO <sub>2</sub>               | HF, HF + NH <sub>4</sub> F                                                 |  |

|--------------------------------|----------------------------------------------------------------------------|--|

| Si <sub>3</sub> N <sub>4</sub> | BOILING 85% H <sub>3</sub> PO <sub>4</sub> @ 180 °C                        |  |

| POLY/SILICON                   | H <sub>2</sub> O+ HNO <sub>3</sub> + HF                                    |  |

| ALUMINUM                       | H <sub>3</sub> PO <sub>4</sub> +HNO <sub>3</sub> +H <sub>2</sub> O @ 30 °C |  |

| GOLD                           | KI + I2 + H2O                                                              |  |

| TITANIUM                       | HF DILUTED                                                                 |  |

| PLATINUM                       | H <sub>2</sub> O + HCl + HNO <sub>3</sub> (ACQUA REGIA)                    |  |

### WET ETCHING FOR WAFER CLEANING

## **SOLVENT CLEANING**

• Methanol, isopropano, acetone Remove organic and metal surface contamination

## **PIRANHA SOLUTION**

• H<sub>2</sub>SO<sub>4</sub> + H<sub>2</sub>O<sub>2</sub> Remove organic and metal surface contamination

## **RCA CLEANING**

- NH<sub>4</sub>OH + H<sub>2</sub>O + H<sub>2</sub>O<sub>2</sub> Remove organic and particles

- HCl + H<sub>2</sub>O + H<sub>2</sub>O<sub>2</sub> Remove metal

- $H_2O + HF$

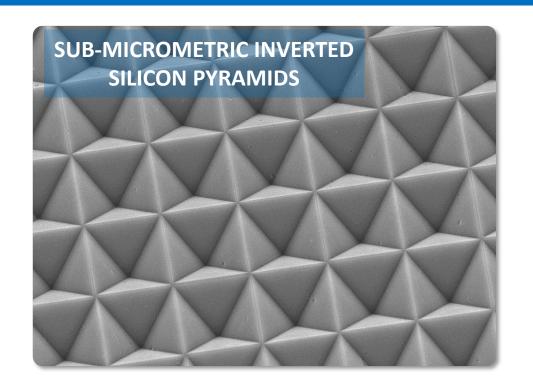

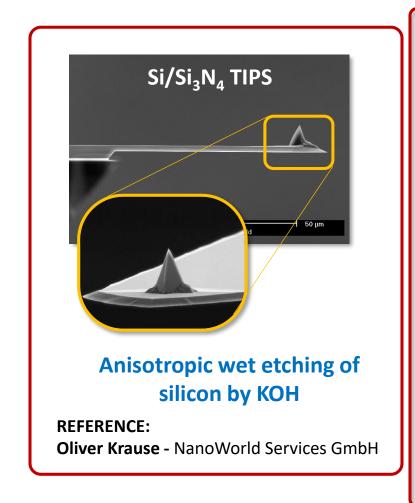

### ANISOTROPIC SILICON WET ETCHING

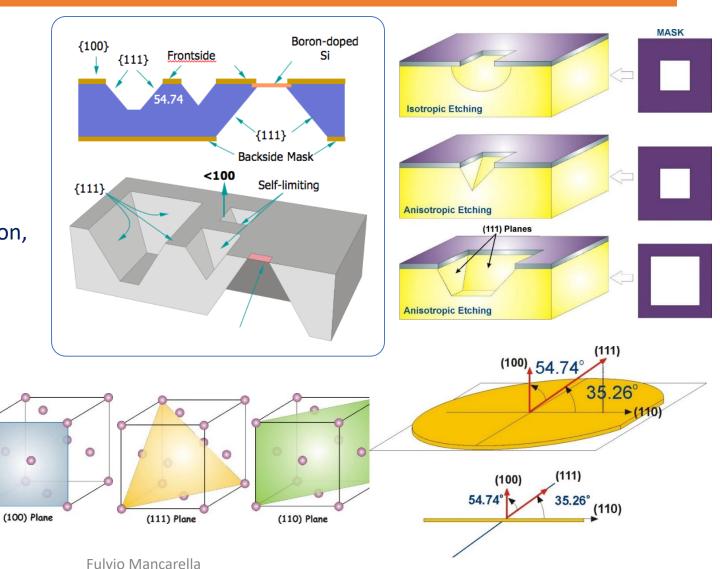

# FORMED BY INTERSECTING {111} PLANE WITH OTHER CRYSTALLOGRAPHIC PLANES.

- Orientation selective etch of silicon occur in hydroxide solutions partly because of the closer packing of some orientations relative to other orientations

- Opensity of planes: <111> > <110>, <100>

- Etch rate: R(111) << R(110), R(100)</p>

- <100> direction etches faster than <111> direction,

with etch rate

- $\circ$  R(100) = few  $100 \times$  R(111)

- It is reaction rate limited

- Used very widely in MEMS (micro electro mechanical systems), since it is inexpensive, fast etching and easy to control.

### **ANISOTROPIC SILICON WET ETCHING**

Of the Hydroxides of Alkali metals, **KOH** is by the most common

KOH etches {111} plane at a rate 100 times slower than it etches {100} plane.

The overall reaction consists of the oxidation of silicon followed of a reduction step:

Si + 2OH

$$^-$$

-> Si(OH)  $^{++}_2$  + 4e  $^-$  (oxidation)

Si(OH) $^{++}_2$  + 4e  $^-$  + 4H  $_2$ O -> Si(OH)  $^{--}_6$  + 2H  $_2$  (riduction)

The etch-rate of silicon is approximately 0.5 to 2  $\mu$ m/min depending on the temperature and concentration of KOH. It is also selective to heavily doped p-type silicon (p++), making common the use p++ doping as etch stop.

Due to the presence of alkali metals inside the etchant, it gives the solution **not CMOS compatible!**

### ANISOTROPIC SILCON WET ETCHING: TMAH

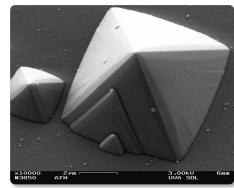

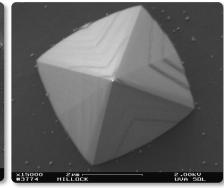

- TMAH ( $(CH_3)_4NOH$ ) etches  $\{111\}$  plane at a rate 30 to 50 slower than  $\{100\}$  plane.

- The etch rate drops by a factor 40 in heavily p-doped silicon

- A disadvantage of TMAH is the occasional formation of undesirable pyramidal hillock at the bottom of the etched cavity.

- Both silicon dioxide and silicon nitride remain virtually unetched in TMAH, and hence can be used as masking layers.

- It is advisable to remove native silicon oxide in HF acid prior to etching in TMAH

- TMAH is an organic material, so it does not contain any metal ions, making TMAH

a potentially IC-compatible etching agent.

|      | ETCH STOP                                                               | ETCH RATE<br>(100)<br>μm/min | ETCH RATE<br>RATIO<br>(100)/(111) | REMARKS                                                           | MASK                                                                                                                       |

|------|-------------------------------------------------------------------------|------------------------------|-----------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| КОН  | <b>B &gt; 10<sup>20</sup> cm<sup>-3</sup></b> REDUCED ETCH RATE BY 20   | 1,4                          | 100                               | IC INCOMPATIBLE, ETCHES OSIDE FAST LOTS OF H <sub>2</sub> BUBBLES | Si <sub>3</sub> N <sub>4</sub> , SiO <sub>2</sub>                                                                          |

| ТМАН | <b>B &gt; 4·10<sup>20</sup> cm<sup>-3</sup></b> REDUCED ETCH RATE BY 40 | 1                            | FROM <b>12.5</b> TO <b>50</b>     | IC<br>COMPATIBLE,<br>Easy to handle                               | SiO <sub>2</sub> etch rate is<br>4 orders of<br>magnitude<br>lower than<br>(100) silicon<br>Si <sub>3</sub> N <sub>4</sub> |

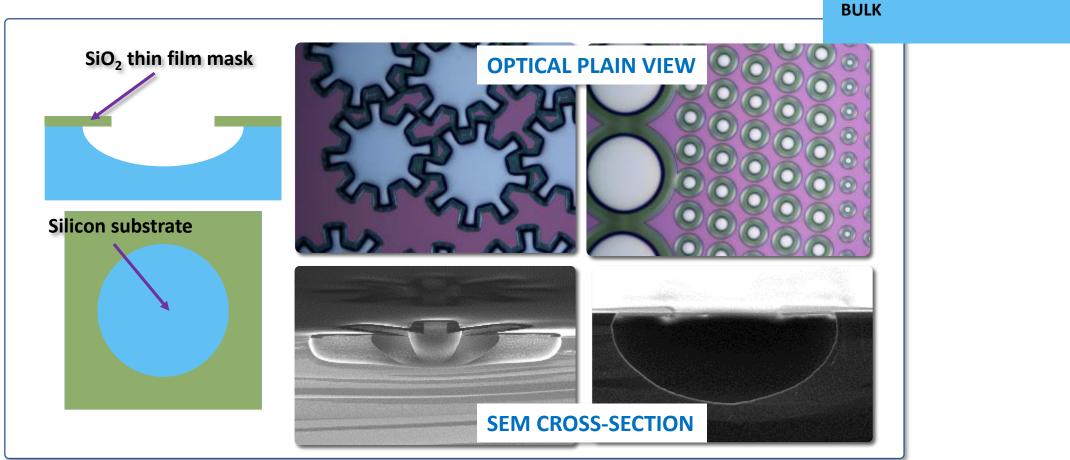

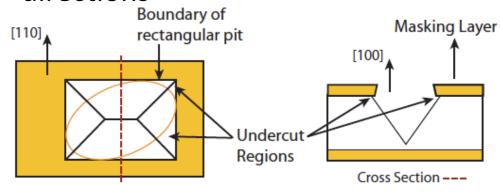

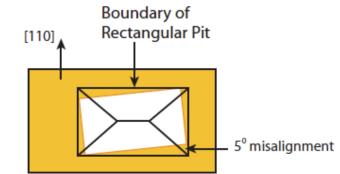

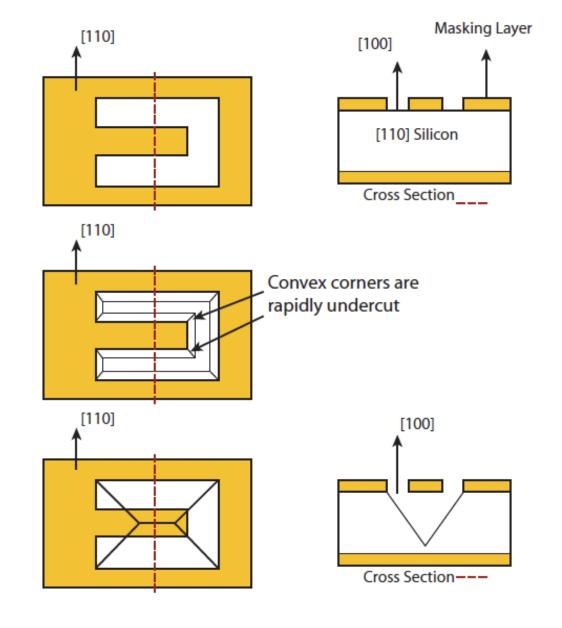

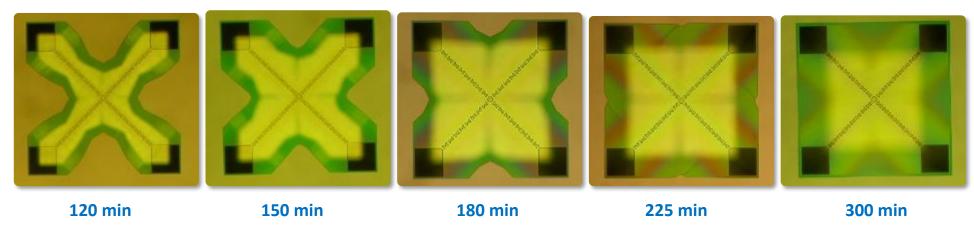

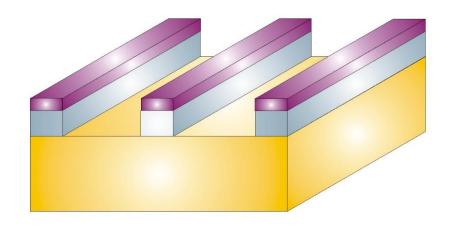

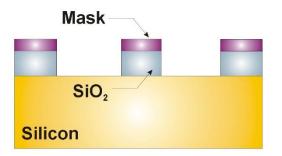

## MAKING A TRENCH WITH KOH/TMAH

Any mask feature, if etched long enough, will result in a V-groove tangent to the mask along <110> directions

Misalignment of the mask relative to the [110] direction always results in a larger etched region

Roundary of

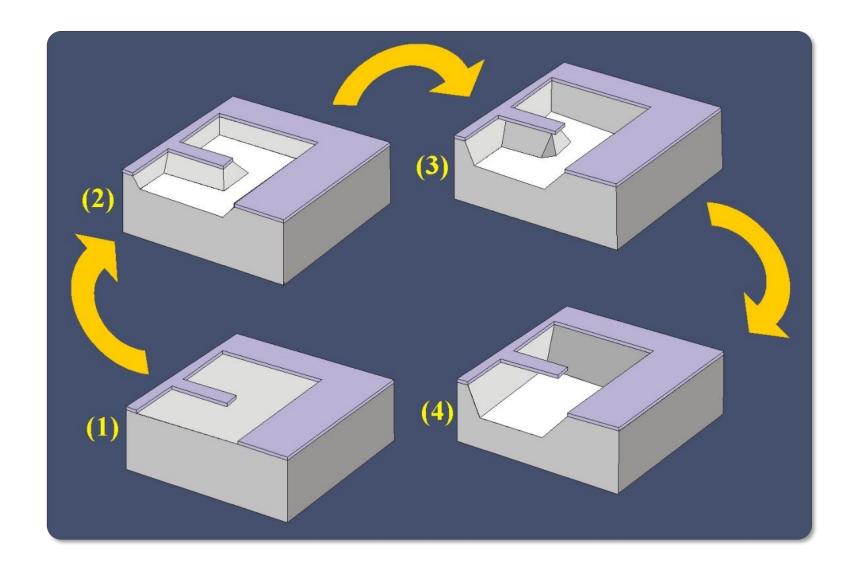

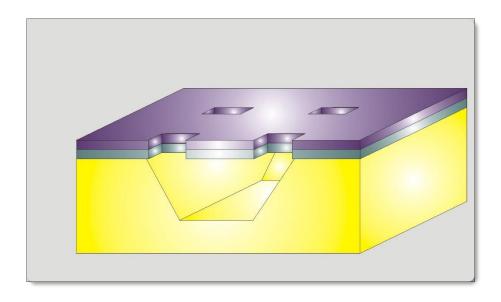

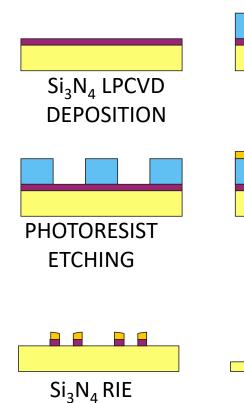

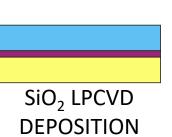

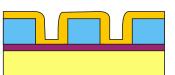

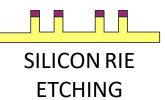

## TMAH ETCHING: Simplified process flow for the realization of a cantilever

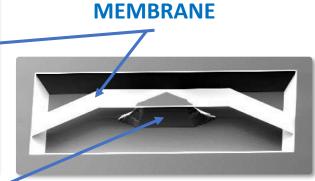

**Deposition of membrane stack**

Lithography to define the membrane

**Etching to realize the holes in the membrane stack**

**Anisotropic Wet silicon etching**

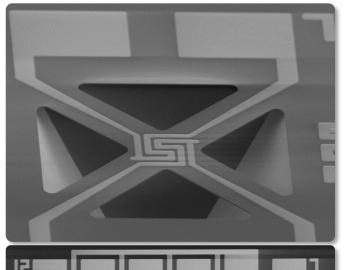

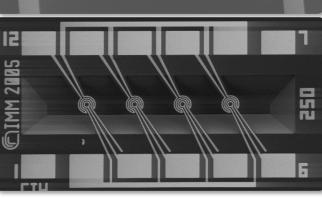

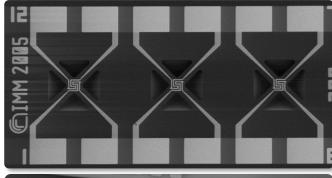

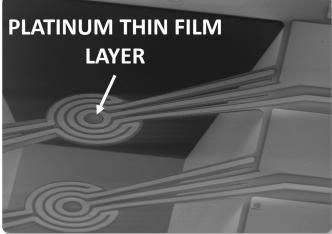

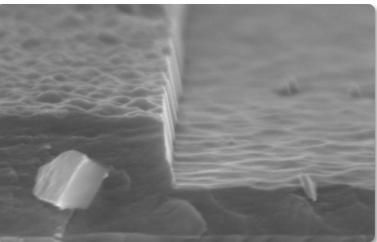

## TMAH ETCHING: SEM IMAGES STRUCTURES AND SUSPENDED MEMBRANE WITH DIFFERENT GEOMETRIES

**SILICON BULK**

DIELECTRIC

The procedure of transfering patterns onto a wafer by wet etching was well established, and the liquid etchant systems are available with very high selectivity.

However, wet etching processes are typically **isotropic**. Therefore, if the thickness of the film being etched is comaprable to the minimum pattern dimension, undercutting due to isotropic etching become <u>intollerable</u>.

One alternative pattern transfer method that offers the capability of non-isotropic (anisotropic) etching is «dry etching».

A considerable effort has been expected to develop dry etch processes as replacements for the wet etch process.

The overall goal of an *dry etch process* for VLSI/MEMS fabrication is to be able to reproduce the features on the mask with fidelity.

This should be achiveable with control of

- Slope of the feature sidewalls

- Degree of undercutting

In addition a useful etch process should have the following characteristics:

- 1. Highly selective against etching the mask layer material

- 2. Highly selective against etching the material under the film being etched

- 3. Etch rate should be rapid

- 4. Etch uniforme across the entire wafer

- 5. Cause minimal damage

- 6. Mask material should be easily removed

- 7. Process should be clean

## A VARIETY OF DRY ETCH PROCESS TYPES EXIST

## PHYSICAL SPUTTERING

- Physical momentum transfer

- Directional etch (anisotropic) possibile

- Poor selectivity

- Radiation damage possible

## **RIE – REACTIVE ION ETCHING**

- Physical (ion) and chemical

- Directional

- More selective than sputtering

## **PLASMA ETCHING**

- Chemical

- Isotropic

- More selective

- Less prone to radiation damage

HIGHER EXCITATION ENERGY

Dry etch processes based on a combination of physical and chemical mechanisms offer the potential of controlled anisotropic etching, toghether with adeguate selectivity

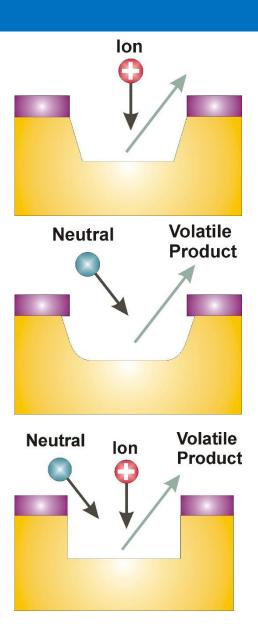

## PHYSICAL ETCHING

positive ions are accelerated and strike substrate with high kinetic energy, some energy is then transferred to surface atoms, which leads to material removal.

## **CHEMICAL ETCHING**

neutral or/and ionized species interact with the material's surface to form volatile products. Chemical etching mechanisms typically etch in a isotropic fashion.

Combination of Chemical and Physical etching (Reactive Ion Etching - RIE)

An anisotropic profile is obtained

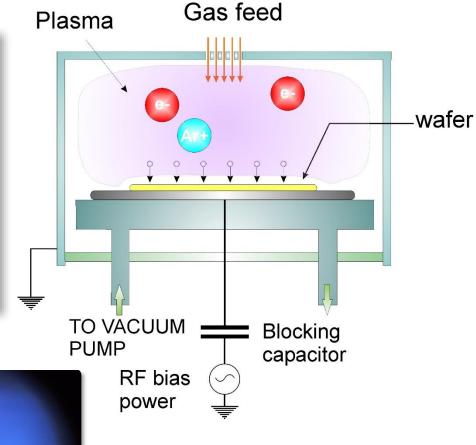

A plasma is fully or partially ionized gas composed of equal numbers of positive and negative charges and a different number of unionized molecules.

A plasma is produced when an electric field of sufficient magnitude is applied to a gas, causing the gas to break down and become ionized.

# PRIMARY PROCESSES OCCURRING IN A **PLASMA ETCH PROCESS** GAS FLOW (1) GENERATION OF ETCHANT SPECIES (6) DIFFUSION IN TO BULK GAS (2) DIFFUSION and TRANSPORT TO SURFACE (3) ADSORPTION (5) DESORPTION **FILM**

An ideal dry etch process based on chemical mechanism can be broken down in to six steps.

## The basic concept of plasma etching is rather direct.

- A glow discarge is utilized to produce chemically reactive species (atoms, radicals, and ions) from a relatively inert molecular gas (or mix of gases)

- The etching gas is selected so as to generate species which react chemically with the material to be etched,

- 3. and whose reaction product with the etched material is **volatile**.

Italian Network for Micro and Nano Fabrication

### **ETCH DIRECTIONALITY IN RIE**

Etching directionality is due to direction energy input into an etching reaction at a surface and can be accomplished by **neutral**, **ion** (i.e. RIE), **electron** and **photon** bombardment of a surface exposed to a chemical etchant.

Plasma etching can be divided in two main groups:

**ION-INDUCED RIE** → reaction-controlled etching

**ION-INHIBITOR RIE** → desorption-controlled etching

#### **ION-INDUCED RIE**

Technique used when the substrate is not etched spontaneously: ions modified the surface reactions in one way or another (e.g. chemical sputtering, chemical enhanced physical sputtering) and make it possible for radical to react with the substrate

e.g: Cl<sub>2</sub>/Si

### **ION-INHIBITOR RIE**

The substrate is etched spontaneously and an **inhibiting layer** is need to achieve directionality.

Sidewalls of thences are not exposed to ion bombardment. The botton of the trench is exposed to ion bombardment thus free from this deposit and etching can proceed.

## <u>Passivation layer can be grown by:</u>

- inserting gases which act as silicon oxidant (Anisotropy < 1)

- Inseting gases which act as polymer precursor (thermally instable)

- Freezing the normally volatile reaction product (cryogenic system)

- Erosion and redeposition of mask material (contamination)

e.g: F/Si, Cl<sub>2</sub>/Al

| MATERIAL                       | ETCH GASES                                                  | ETCH PRODUCTS                                                            |  |

|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|--|

| SILICON/POLYSILICON            | $SF_6 + O_2$<br>$SiCl_4$<br>$Cl_2 + BCl_3$                  | SiF <sub>4</sub><br>SiCl <sub>4</sub><br>SiCl <sub>4</sub>               |  |

| SiO <sub>2</sub>               | CHF <sub>3</sub> + Ar<br>CF <sub>4</sub> + H <sub>2</sub>   | SiF <sub>4</sub> + CO <sub>2</sub><br>SiF <sub>4</sub> + CO <sub>2</sub> |  |

| Si <sub>3</sub> N <sub>4</sub> | $CHF_3 + Ar$ $CF_4 + H_2$ $SF_6 + O_2$                      | SiF <sub>4</sub> + NO <sub>x</sub>                                       |  |

| ALUMINUM                       | Cl <sub>2</sub> + BCl <sub>3</sub><br>Cl <sub>2</sub> + HBr | AlCl <sub>3</sub> , Al <sub>2</sub> Cl <sub>6</sub>                      |  |

| ORGANIC                        | O <sub>2</sub> , CF <sub>4</sub>                            | CO, CO <sub>2</sub> , HF                                                 |  |

### FLUORINE-BASED PLASMA: ANISOTROPIC SILICON ETCHING

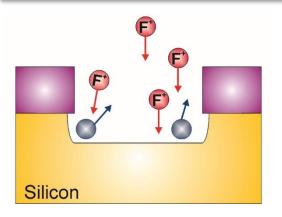

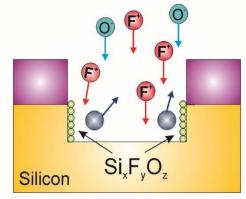

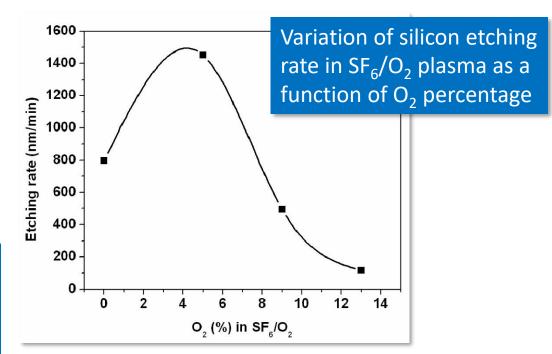

## **ION-INHIBITOR RIE**

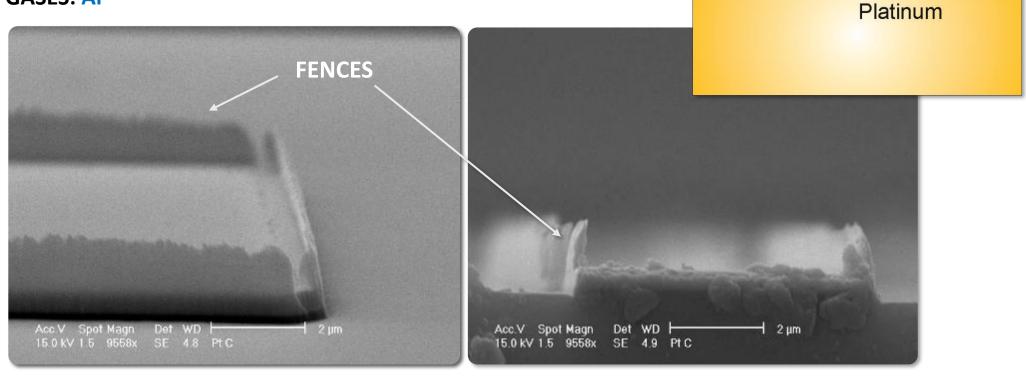

GASES: SF<sub>6</sub>, O<sub>2</sub>

**SF**<sub>6</sub>: substrate is etched spontaneous

O<sub>2</sub>: Act as Si oxidant (Passivation layer)

Si<sub>x</sub>F<sub>y</sub>O<sub>z</sub> inhibitor layer

The  $SF_6/O_2$ -Si system is an ion-inhibitor process. In this gas system oxygen covers the silicon surface with silicon oxide and the  $SF_5^+$  ions etch the passivation layer making it possible for the  $F^*$  radicals to etch the silicon substrate.

Mat. Res. vol.21 no.5 São Carlos 2018 Epub July 10, 2018

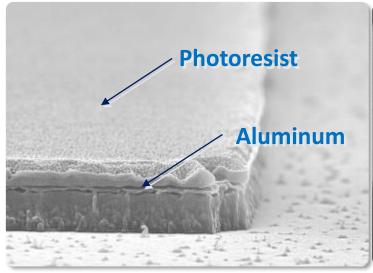

## CHLORINE-BASED PLASMA: THIN FILM ALUMINUNM DRY ETCHING

## **ION-INHIBITOR RIE**

## Passivation layer

Erosion and redeposition of mask material

GASES: Cl<sub>2</sub>, BCl<sub>3</sub>, Ar

BCl<sub>3</sub>: to remove fastly and reproducibly the aluminium oxide layer

Cl<sub>2</sub>: enhances the etch rate of the aluminium

**Ar**: Stabilizes the plasma

- Aluminum is <u>spontaneously</u> etched by Cl<sub>2</sub>

- Surface of aluminum is always protected by a native aluminum oxide layer a few nanometers thick

- Ion bombardment is essential for Al etching

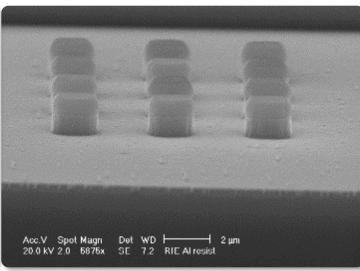

## **ION-INDUCED RIE**

## Passivation layer

Erosion and redeposition of mask material

GASES: SiCl<sub>4</sub>

**ETCH PRODUCT: SiCl<sub>4</sub>**

Problem: excess passivation.

The sidewall profile is not vertical

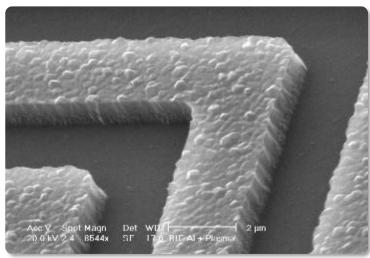

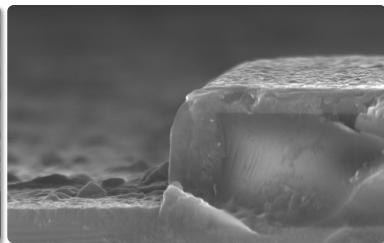

- Platinum has been physically etched by argon plasma.

- The fences are due to platinum redeposited on the sidewall.

**GASES: Ar**

**Photoresist**

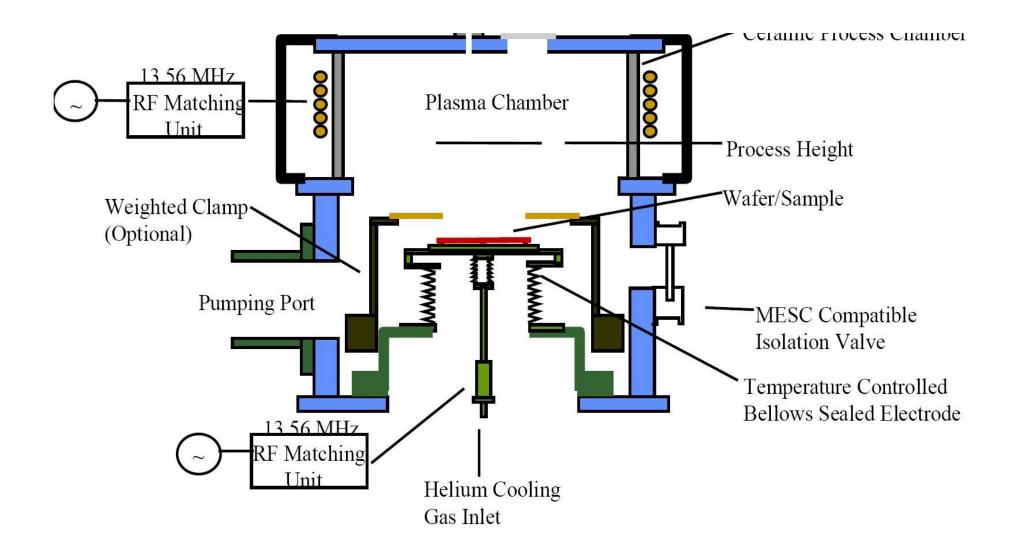

RIE (CCP - capacitively coupled plasma) are able to etch silicon and other material slowly

How to increase the etch rate?

## **INCREASING THE DENSITY OF PLASMA**

**Inductively Coupled Plasma** (ICP) RIE

In this type of system, the plasma is generated with an RF powered magnetic field. Very high plasma densities can be achieved

A combination of parallel plate and inductively coupled plasma RIE is possible. In this system, the ICP is employed as a high density source of ions which increases the etch rate, whereas a separate RF bias is applied to the substrate (silicon wafer) to create directional electric fields near the substrate to achieve more anisotropic etch profiles

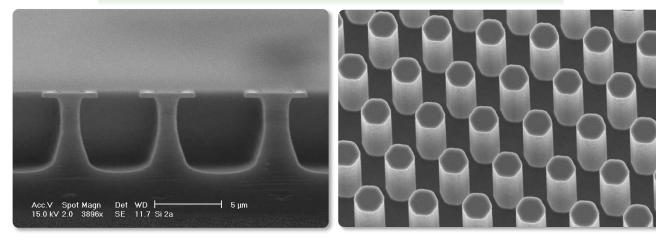

### **DEEP REACTIVE ION ETCHING**

## There are two main technologies for high-rate DRIE

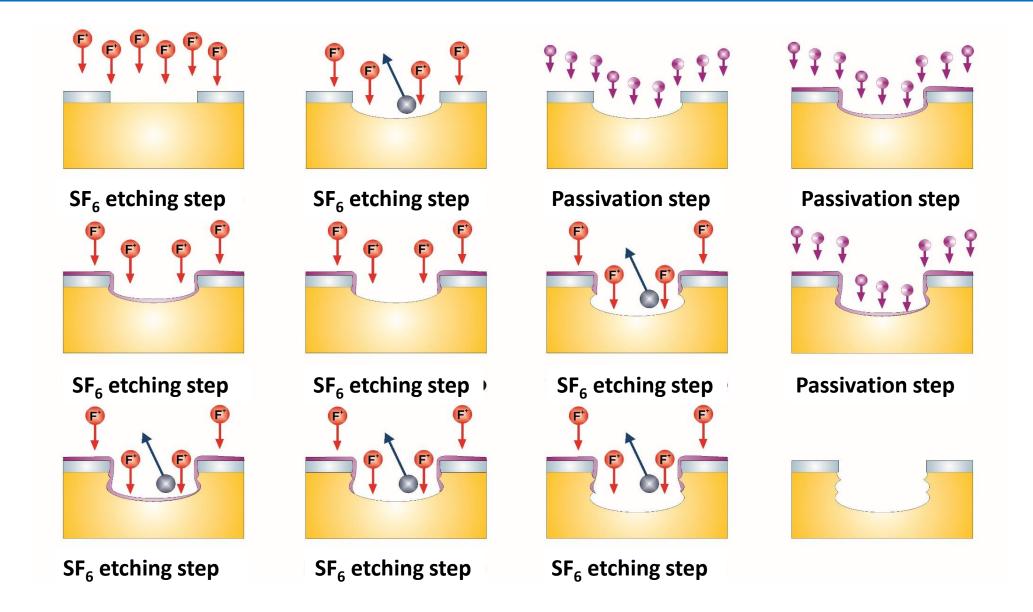

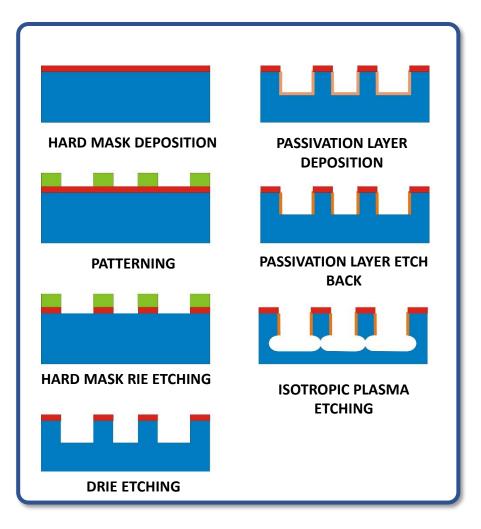

## **BOSCH** PROCESS

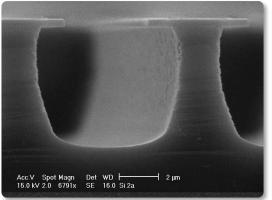

Anisotropic reactive ion etching involves the delicate balance between passivation of the sidewalls and etching of the bottom of the structures. The etch is mainly produced by bombardment of ions from the plasma discharge. Lærmer and Schilp first developed this etch technique at Bosch and hence it is also commonly referred to as the "Bosch process." This technique involves alternating etch and passivation steps in a continuous cycle to achieve the high aspect-ratio structures. Both steps are done at room temperature

### **CRYOGENIC PROCESS**

An alternative technique introduced by Tachi *et al.* involves etching substrates at cryogenic temperatures, also using fluorine-based high-density plasmas. The main chemical reactions that occur in reactive ion etching are those due to spontaneous etching and those due to ion-assisted reactions. The spontaneous reactions which occur on both the sidewalls and the bottom account for the isotropic etch. To produce anisotropic etches the spontaneous reaction has to be slowed considerably. Tachi *et al.* accomplished this by controlling the substrate temperature, the rationale being that cooler temperatures will reduce the reaction probability or the incident flux of radicals on the sidewalls

## **BOSCH PROCESS: PRINCIPLE**

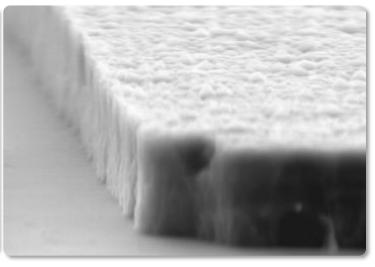

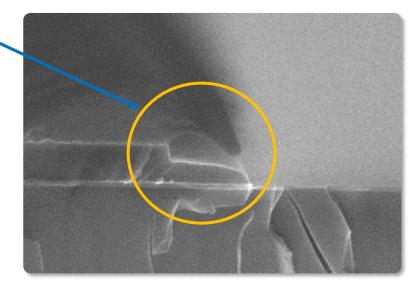

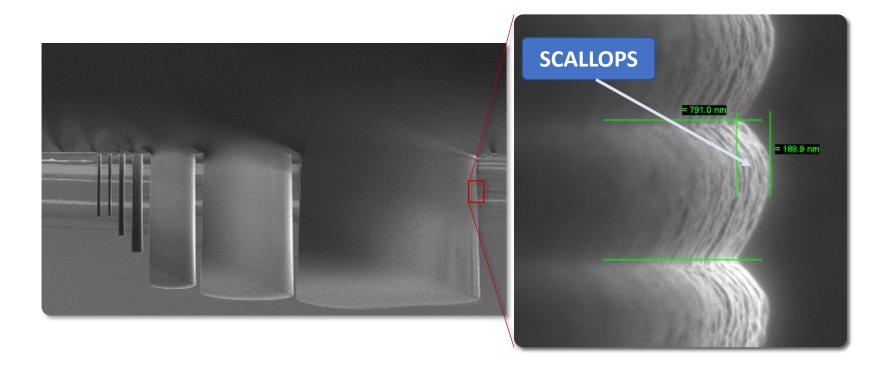

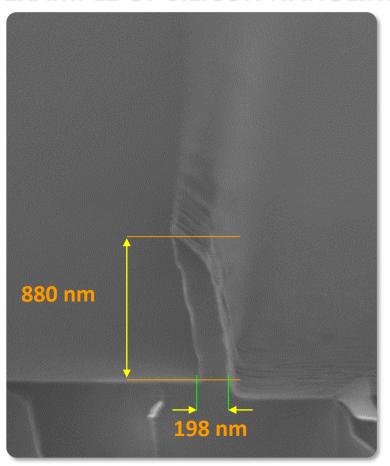

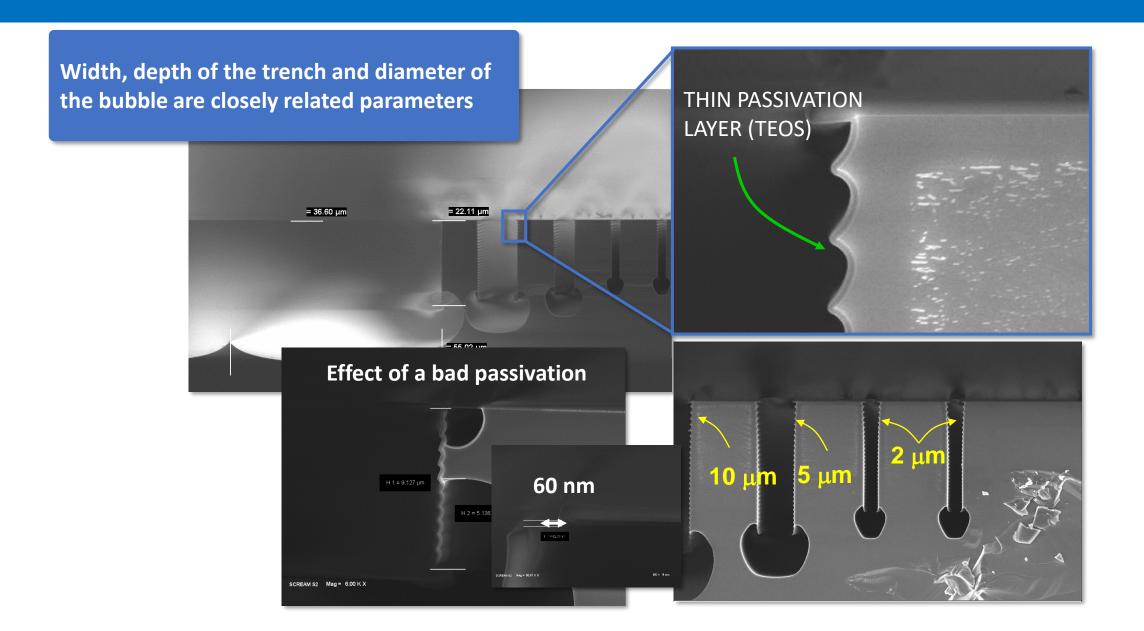

## **BOSCH PROCESS DEEP RIE ETCHING: SIDEWALL QUALITY**

Surface roughness issues are particularly important in BOSCH tools. Because of alternate etching and passivating cycles and the spontaneous nature of the etch in fluorinated chemistries, structures fabricated using BOSCH process exhibit a characteristic scalloped sidewall roughness that can be unacceptable in some applications.

It is possible to minimize the depth of those scallops by varying the operation conditions during dry processing. The depth of the scallops is due mostly to the spontaneous etching of silicon by fluorine.

### **MACRO-LOADING**

# Etch rate for a given process becomes slower with more exposed etch area

- Etch rate is limited by the arrival of neutrals (neutral limited regime)

- Is a function of total exposed area reacting with gas phase species

- Center to edge uniformity variations can be a result of macro loading

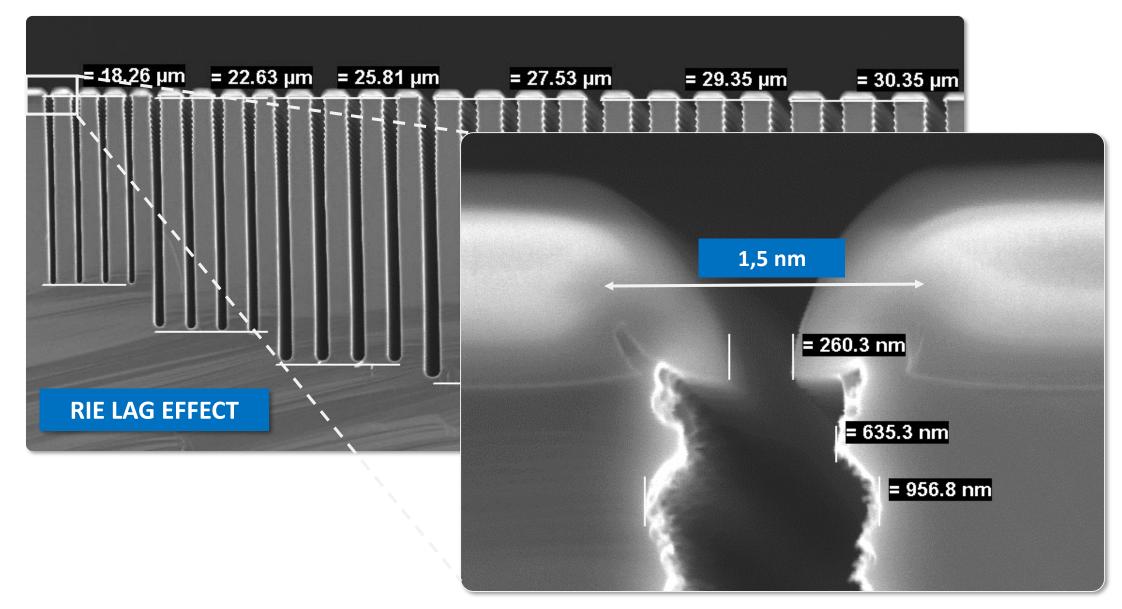

## MICRO-LOADING AND RIE LAG

## Smaller features etch slower than larger features.

Gas conductance indeep narrow holes is low and the reactants simply can not reach the bottom effectively (or the reaction products removed). Ion bombardment is also affected: ions experience sidewall collisions indeep the strucures, and bombardment at the bottom is reduced. These effects lead to a reduced etch rate indeep structures of high aspect ratio. RIE lag is not related to RIE reactors; it is presenting all plasma etching systems irrespective of actual reactor design

### **BOWING**

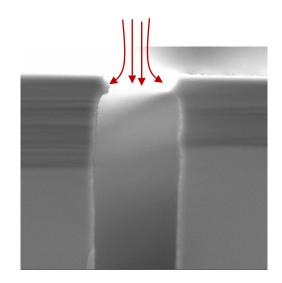

Ion bowing is caused by the diffraction of ions while entering a trench/needle or by the negative potential of trench walls (needle wall) with respect to the plasma glow resulting in a deflection of these ions to the wall.

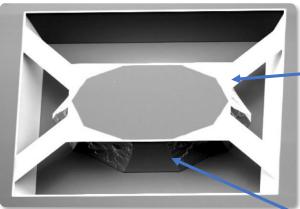

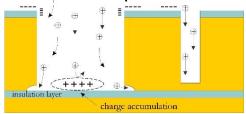

### **NOTCHING**

When the silicon etching end point is reached, the underlying oxide (either oxide on the back side of a bulk wafer, or BOX) becomes charged. This charging leads to repellency of incoming ions, and they are deflected side ways, enhancing lateral etching near the silicon/oxide interface. Note that RIE lag has an effect on **notching**: the larger feature shave experienced longer overetching, therefore the notching effect has had more time to operate.

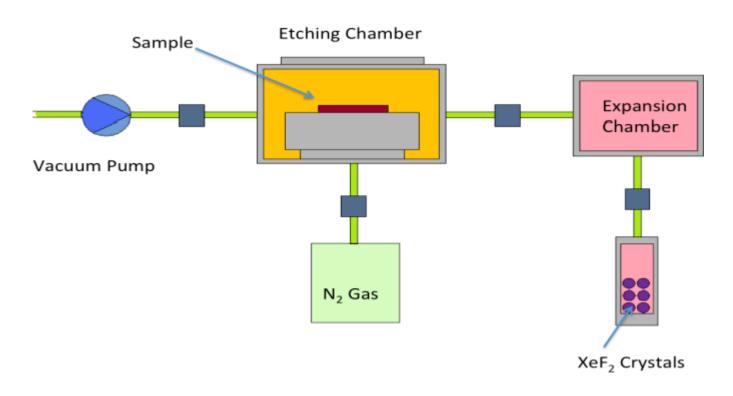

For the purpose of silicon etching, it is not even necessary to use a plasma source of fluorine radicals. A number of gaseous compounds are well known for the ability to etch silicon spontaneously, without need for plasma excitation. XeF<sub>2</sub> deliver fluorine radicals which once abdorbed onto the surface.

The reaction is exothermic and may result in an increase of temperature. This effect is mitigated by the use of **pulsed** rather than continuous etch system.

37

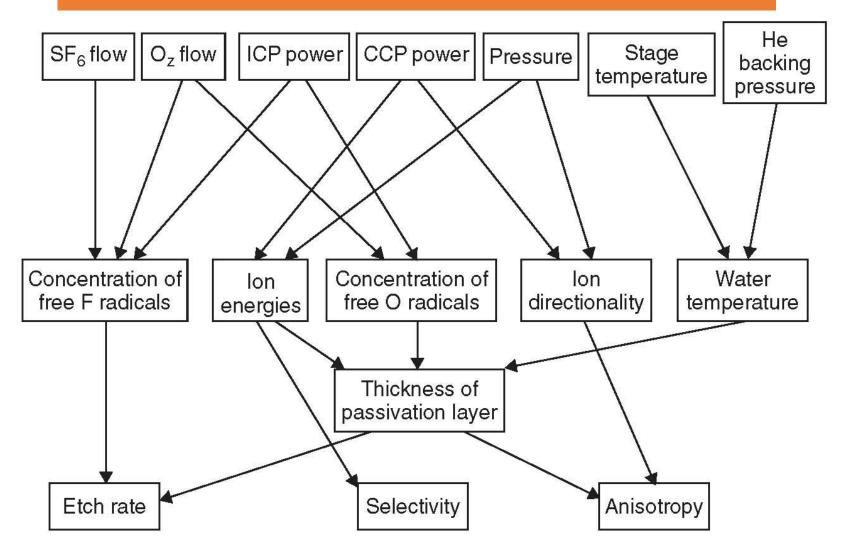

# THE INTERDEPENDENCE OF REACTOR PARAMETERS TO PLASMA PARAMETERS AND ETCH RESPONSES ON A WAFER

## **TIPS & TRICKS**

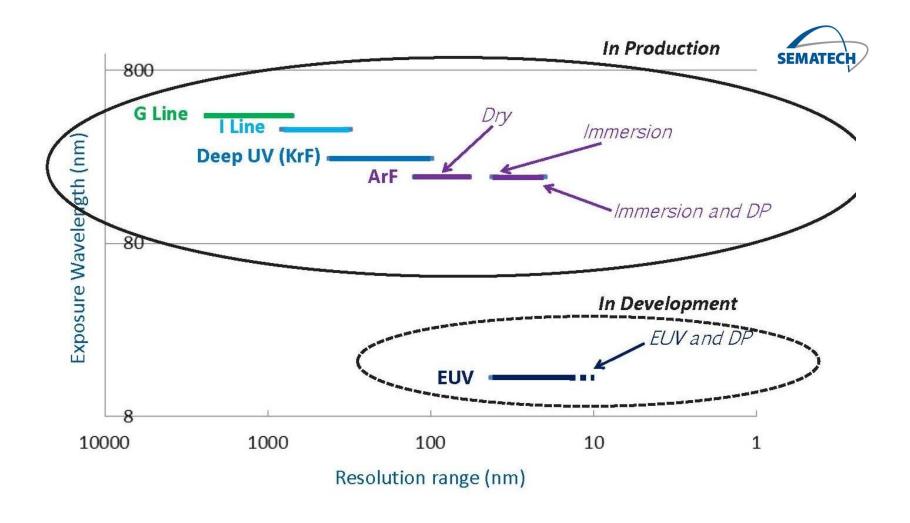

#### IMPROVEMENT THROUGH LITHO WAVELENGTH AND NA

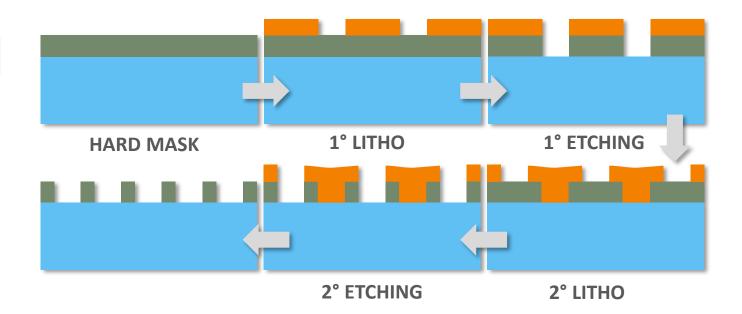

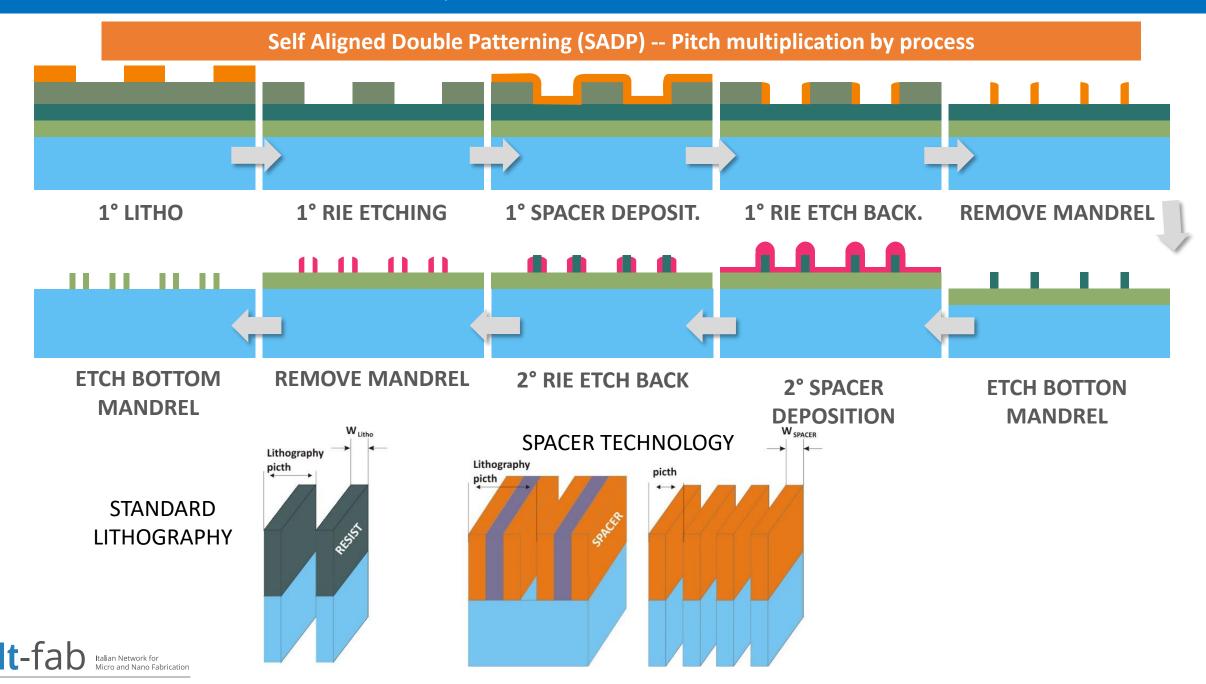

#### **DOUBLE PATTERNING**

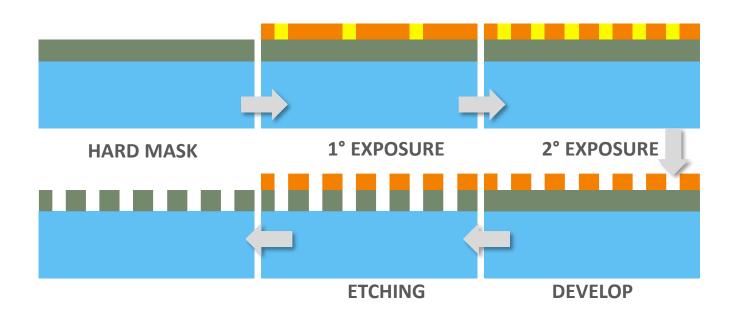

#### **DOUBLE EXPOSURES**

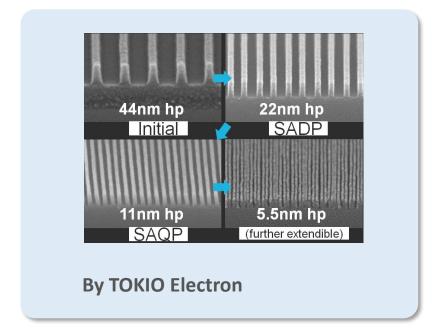

#### **SELF ALIGNED DOUBLE PATTERNING TEHCNIQUE**

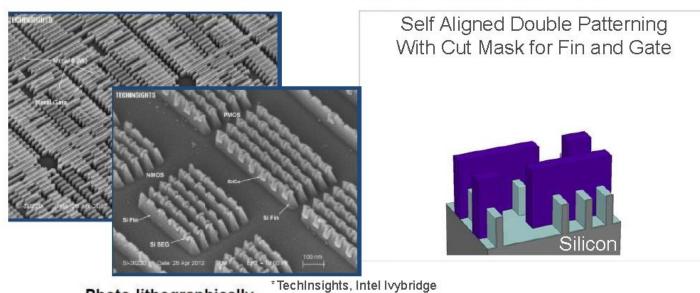

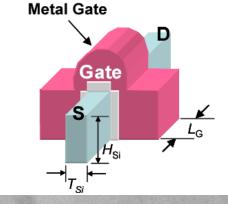

#### FinFET Formation – Scalable to 10nm w/o EUV

Photo-lithographically defined sacrificial structures

1st Spacers

**SELF-ALIGNED MULTIPLE PATTERNING**

**By Applied Materials**

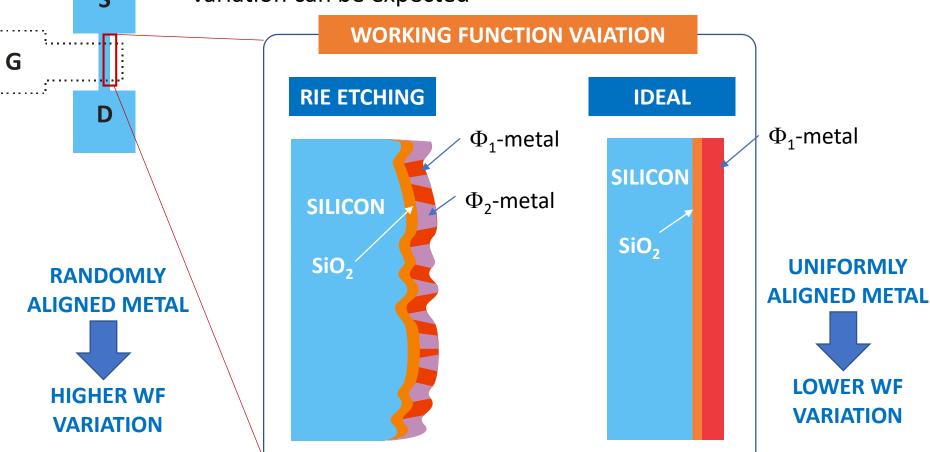

#### **V<sub>TH</sub> VARIATION FOR MG FINFETS**

Rough etched side wall causes randomly aligned metal grain and thus higher WF variation

If side wall is flat, uniformly aligned metal grain and thus lower WF variation can be expected

45

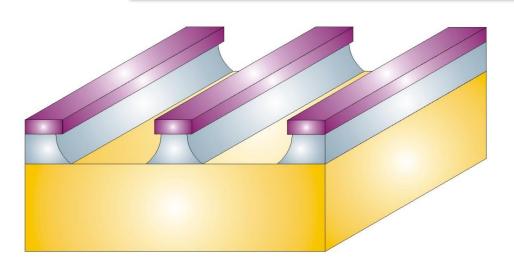

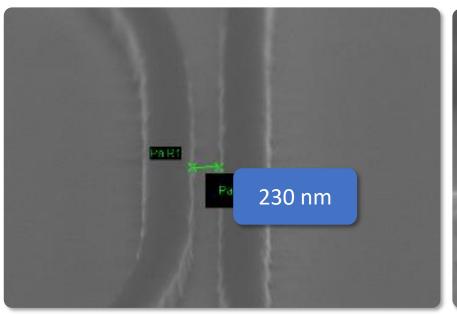

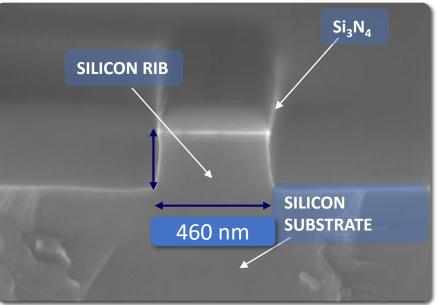

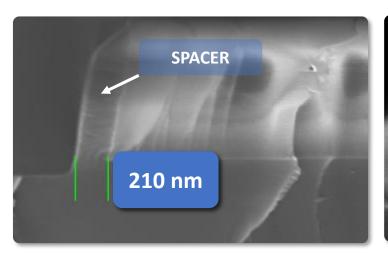

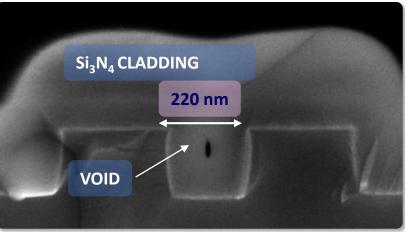

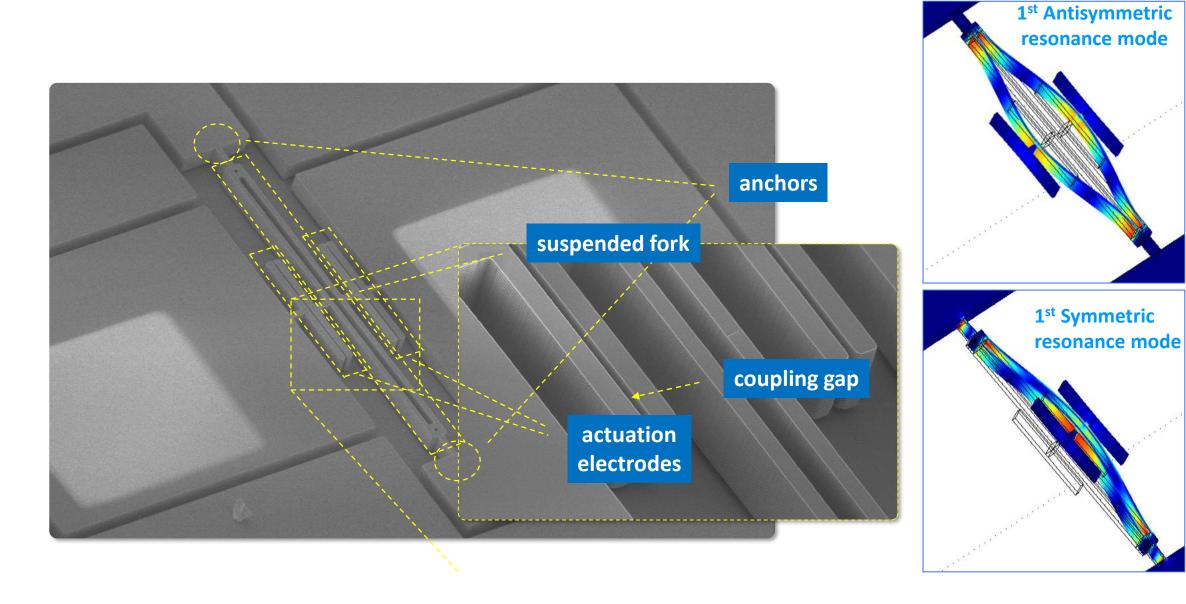

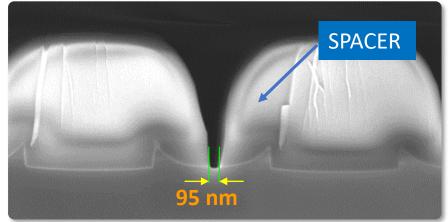

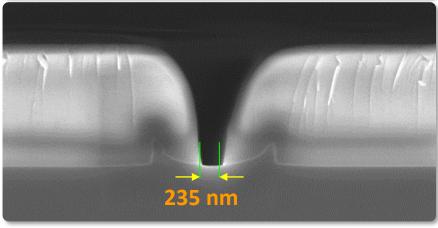

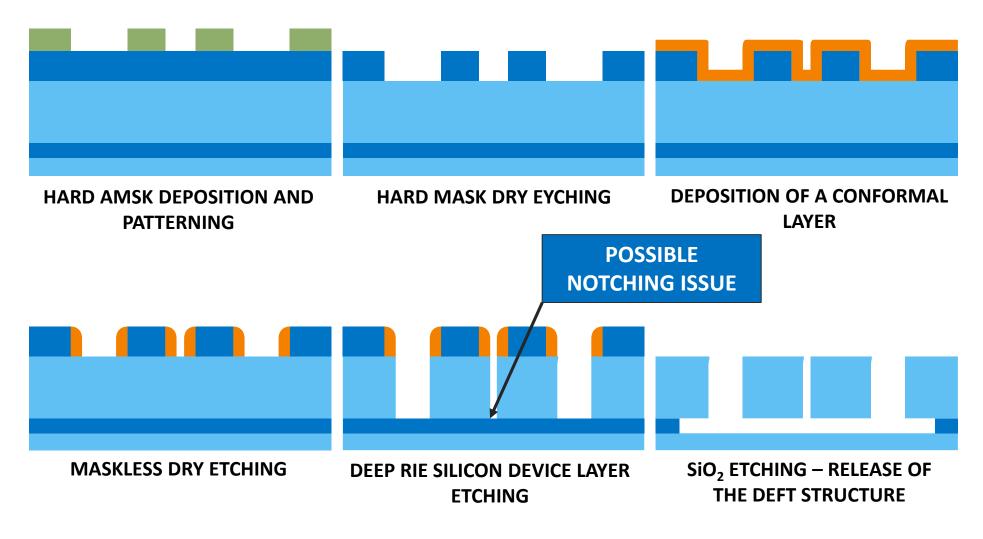

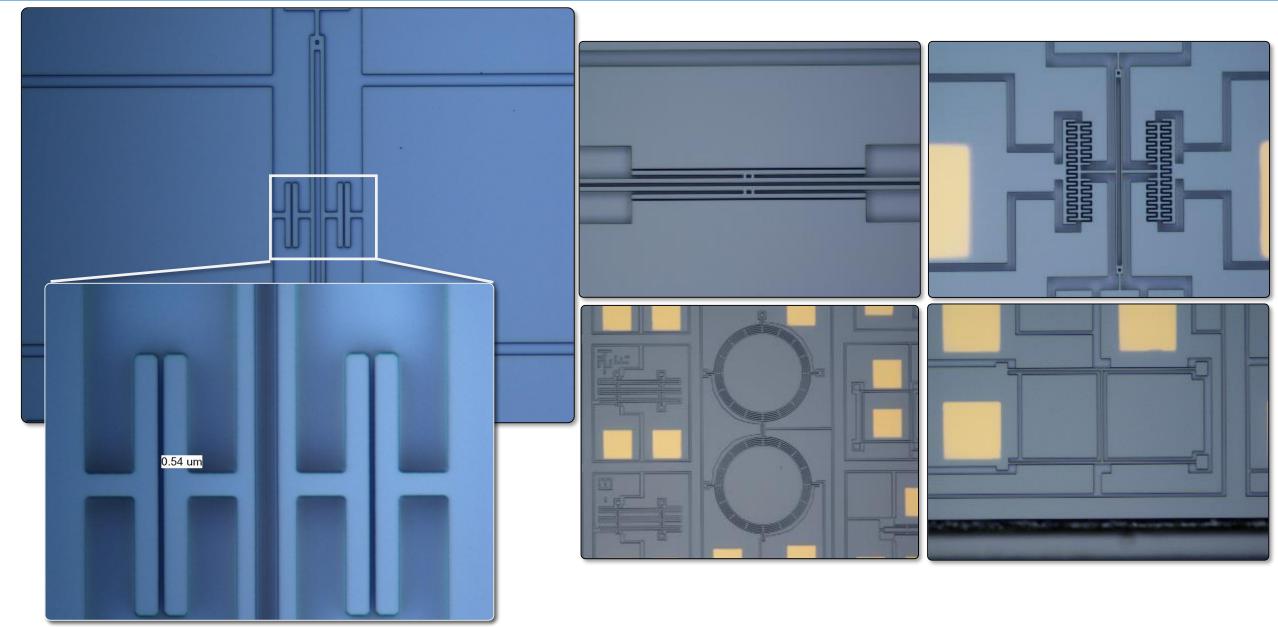

#### **MICROFABRICATION OF THE NANOMETRIC STRUCTURES**

- Standard CMOS process: near-UV lithography, chemical vapor deposition (CVD), reactive ion etching (RIE)...

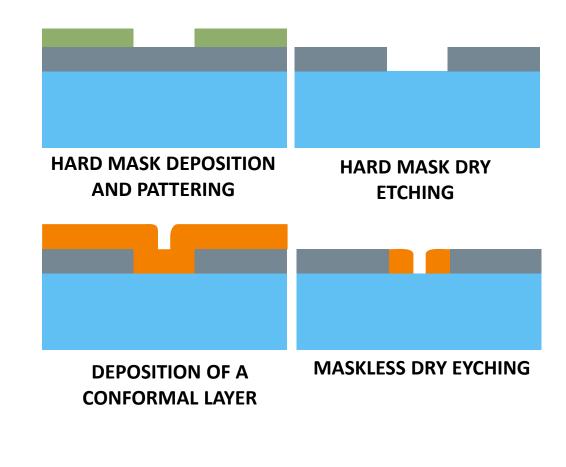

- >Spacer techniques allowed for the definition of submicron features and gaps of the coupling structures

- > Features down to 300 nm with conventional micrometric lithography

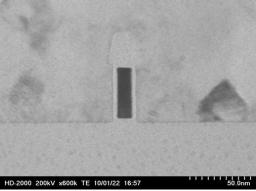

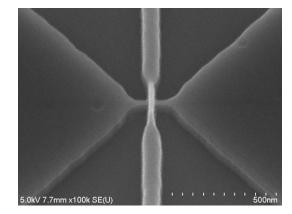

#### **EXAMPLE OF SILICON NANOLINE**

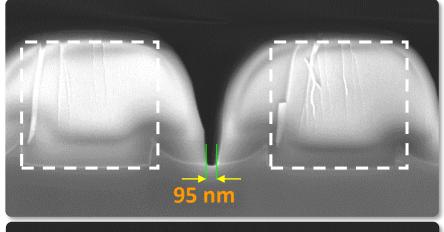

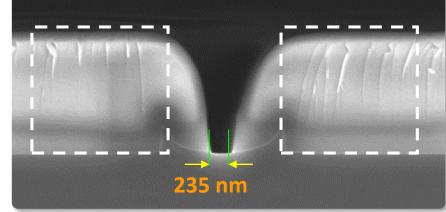

#### **EXAMPLES OF NANO-GAP**

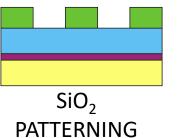

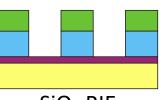

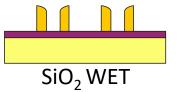

#### **SILICON PHOTONICS by SPACER TECHNOLOGIES**

DEPOSITION CONFORMAL LAYER

RIE MASKLESS (ETCHBACK)

SiO<sub>2</sub> RIE ETCHING

**ETCHING**

**ETCHING**

#### **SILICON PHOTONICS by SPACER TECHNOLOGIES**

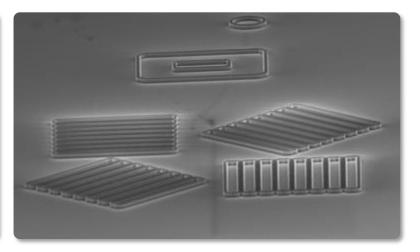

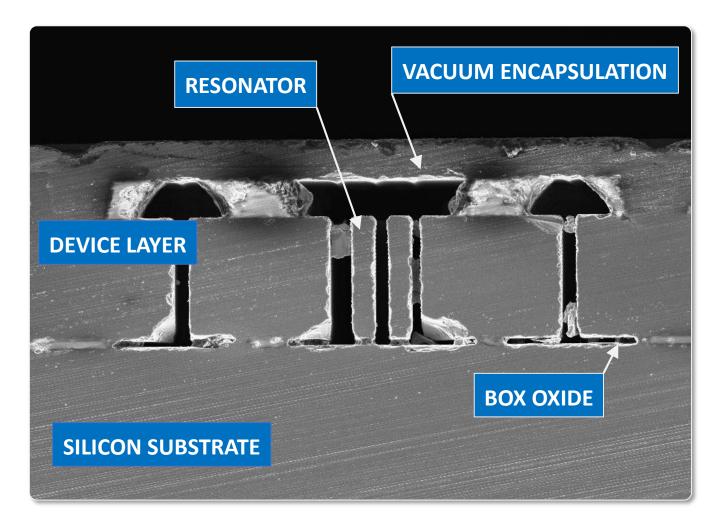

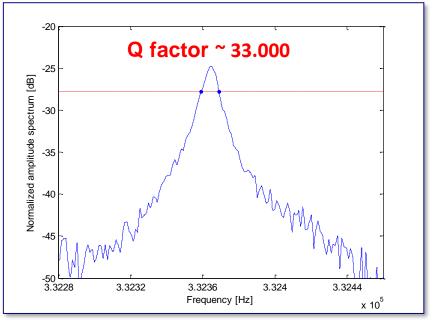

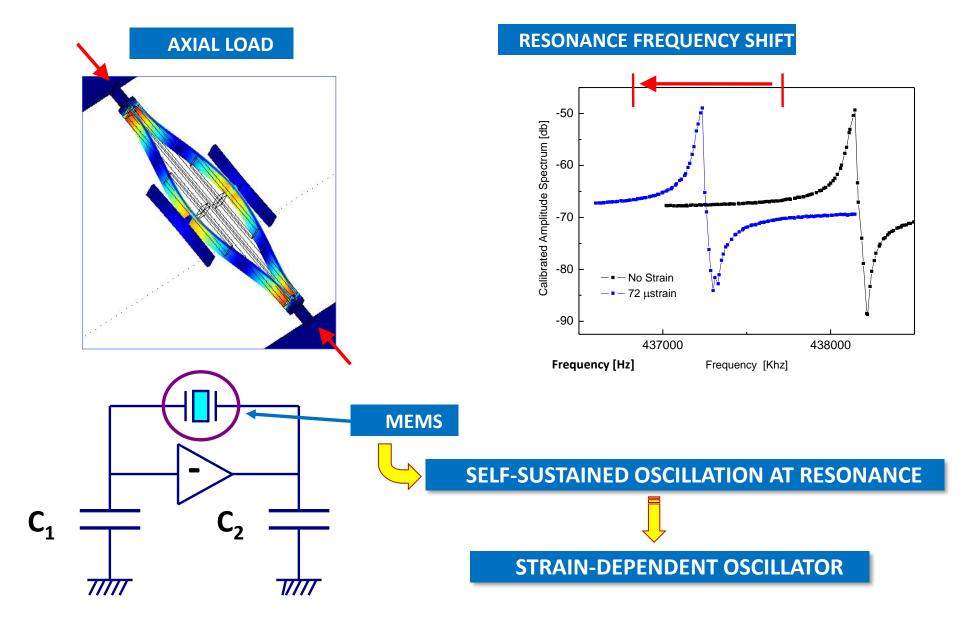

# RESONANT MEMS STRAIN SENSORS

#### **EXAMPLES OF NANO-GAP**

#### Silion-On-Insulator (SOI) TECHNOLOGIES

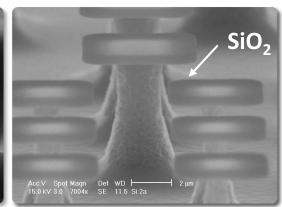

#### **DEEP RIE SILICON DEVICE LAYER ETCHING**

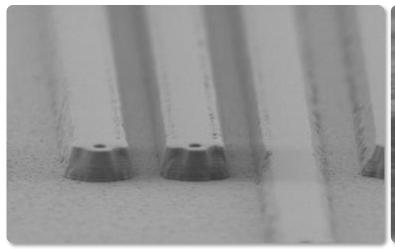

#### MEMS FABRICATION: RESONATORS WITH VARIOUS GEOMETRIES

t-fab Italian Network for Micro and Nano Fabrication

#### **MEMS RESONATORS AS STRAIN SENSORS**

# COMBINATION OF ISOTROPIC/ANISOTROPIC SILICON DRY ETCHING FOR MICROFLUIDIC APPLICATIONS

57

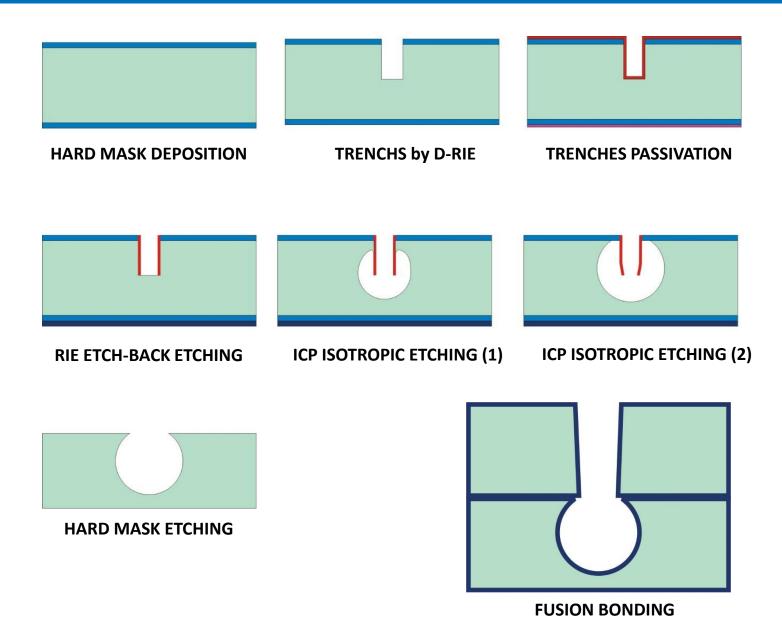

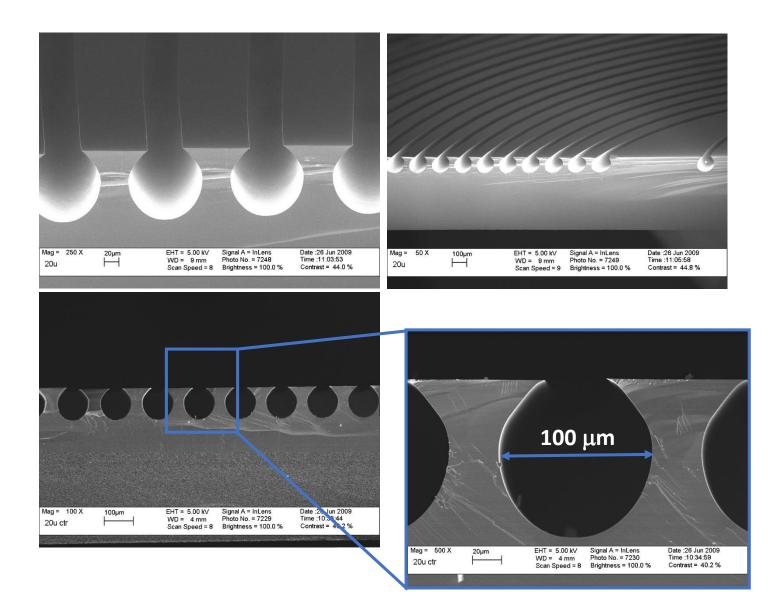

#### COMBINATION OF ISOTROPIC/ANISOTROPIC SILICON DRY ETCHING FOR MICROFLUIDIC APPLICATIONS

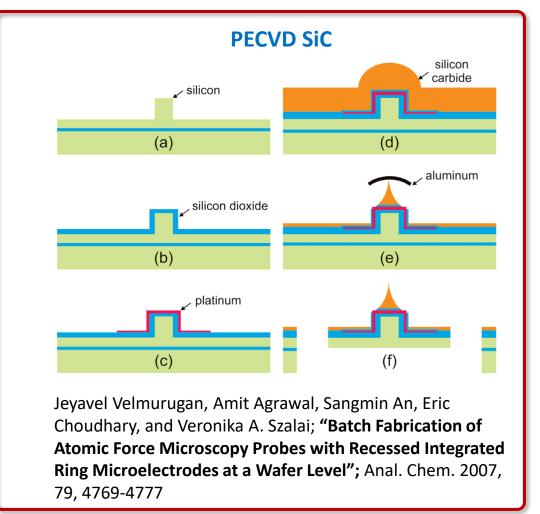

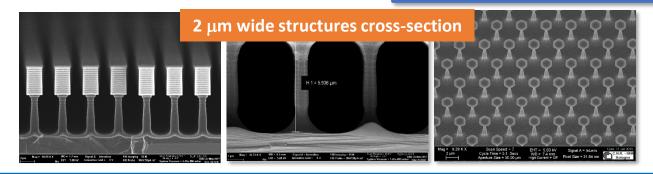

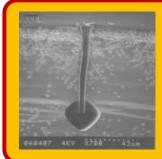

#### **ATOMIC FORCE MICROSCOPE TIPS**

58

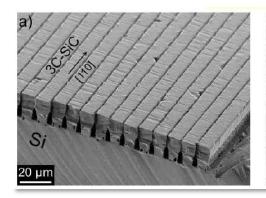

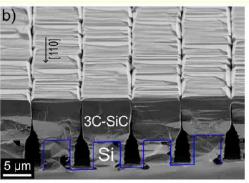

#### ISO/ANISO DRY ETCHING IN ADVANCE MATERIAL

Toolbox of solutions for the reduction of defects in bulk cubic silicon carbide material

Proposed a new approach to improve the quality and to reduce stress modifying the structure of the substrate (compliance substrate) in order to force the system to reduce the defects while increasing the thickness of the layer

#### **«CHALLENGE» H2020 EUROPEN PROJECT**

3C-Si etero-epitaxilly grown on silicon compliance substrates and new 3C-SiC substrates for sustainable wide-band-gap power devices

www.h2020challenge.ue

Circular channel etched electrochemically in an 5% aqueous HF solution

Circular channel obtained after wet chemical etching in HF-HNO<sub>3</sub> solution

V-groove channel obtained after KOH etching

Pear-shaped channel, obtained by isotropic RIE

#### «Micromachining of buried micro channels in silicon»,

De Boer, M.J.aEmail Author, Tjerkstra, R.W.b, Berenschot, J.W.a, Jansen, H.V.c, Burger, G.J.d, Gardeniers, J.G.E.a, Elwenspoek, M.a, Van Den Berg, Journal of Microelectromechanical Systems, Volume 9, Issue 1, March 2000, Pages 94-103

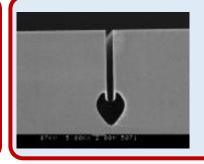

The gas-chromatographic separation principle: Based on specific affinity between sample and "stationary phase"

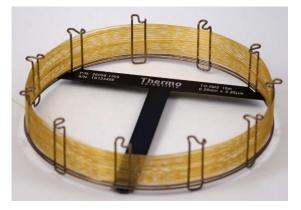

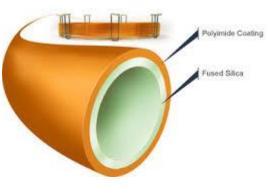

## STANDARD FUSED SILICA COLUMN FOR GAS CHROMATOGRAPHY

Stationary Phase

Fused Silica

Polyimide Coating

The uniformity of the steady-phase thickness is one of the constraints for achieving better separation and resolution

**FAST-GC**: guarantee <u>fast analysis</u> cycles, minimal dead volumes, low costs and high portability for in-field use.

DEVELOPING AND

MANUFACTURING OF A

MEMS BASED CIRCULAR GC

COLUMN FOR FAST-GC

COMBINATION OF ISOTROPIC/ANISOTROPIC SILICON DRY ETCHING

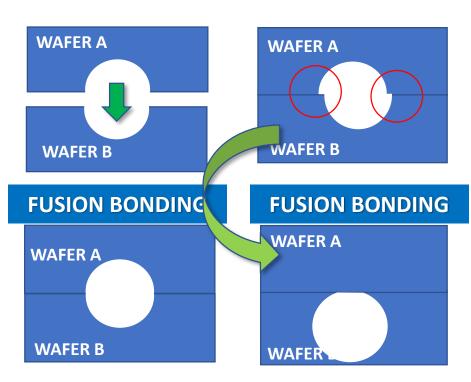

#### SILICON CHANNELS WITH CIRCULAR CROSS-SECTION

#### **SCREAM PROCESS**

- ✓ First demonstrated by MacDonald's group at Cornell University

- ✓ Single crystal silicon (SCS) microstructures

- ✓ Post-CMOS process for electronics integration

### TRENCH SIDEWALL PASSIVATION LAYER

- THERMAL SILICON OXIDATION

- LPCVD CONFORMAL THIN LAYER

- PLASMA POLYMERIZED

FLUOROCARBON THIN

(USING PASSIVATION STEP OF

A BOSCH PROCESS CYCLE)

- PARYLENE THIN LAYER

#### **BURRIED CIRCULAR CHANNEL: SIMPLIFIED PROCESS FLOW**

# THANK YOU FOR YOUR ATTENTION